# FOR RADIO SHACK SERVICE CENTERS **TRS-80** Technical Manual

CUSTOM MANUFACTURED IN U.S.A. BY RADIO SHACK TANDY CORPORATION

All rights reserved. Reproduction or use, without express permission, of editorial or pictorial content, in any manner, is prohibited. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

> © Copyright 1978, Radio Shack, A Division of Tandy Corporation, Fort Worth, Texas 76102, U.S.A.

Printed in the United States of America

# TABLE OF CONTENTS

#### TITLE

#### INTRODUCTION

"We've done so much, with so little, for so long, that now we can do anything, with nothing, except weld the Crack of Dawn and put wheels on a Carriage Return!"

Armed with only a schematic, attacking a TRS-80 computer can be like trying to weld that crack. You may know what "CPU" stands for. You may have the knowledge of how a microprocessor system works. So you grab the schematic's book and attack that TRS-80 with soldering iron smoking and a determined gleam in your eye.

After a while, you find you have problems. You know a 4K RAM needs 12 address lines. But you only found 7. You know a computer keyboard gives you ASCII. Yet, you find the keyboard is shorting out an address line to a data line. You know how a TV typewriter scrolls characters on the screen, and you do find the video memory wired to do the job. But where is all the hardware to make the display scroll?

You know what a NAND gate symbol looks like and you also know what an OR gate symbol looks like. But some sadist has gotten all his symbols backwards. A NAND gate is shown like an OR gate, and the OR gate looks like a NAND gate. To top it all off, the power supply consists of two large rectangles with transistors and resistors sticking out of them; and the only voltages shown are the resulting outputs. Welcome to the wonderful world of computer electronics.

Now admit it. You don't really know your ASCII from a scroll when it comes to the TRS-80 computer.

The purpose of this manual is to give you a practical knowledge of system operation as it pertains to the TRS-80. This manual will show you why there are only seven address inputs to a 4K RAM. You will be shown when the microprocessor inputs data from the keyboard the CPU thinks the keyboard is a memory, of all things! You'll learn how the CRT screen is scrolled and you might even learn to appreciate the backward symbolization. As far as the power supply is concerned, you might find that it's not nearly as complex as you thought. So, grab your schematics and let's take a tour of the TRS-80 computer.

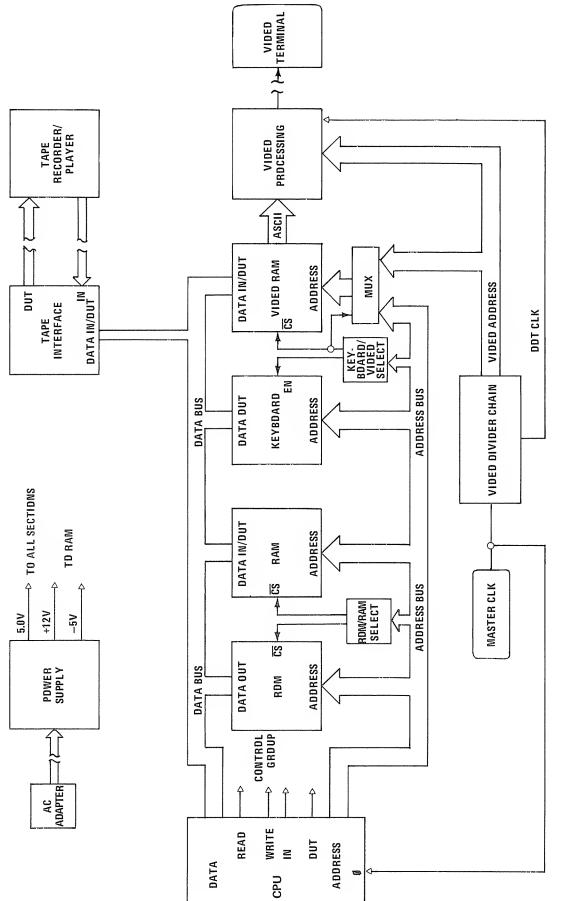

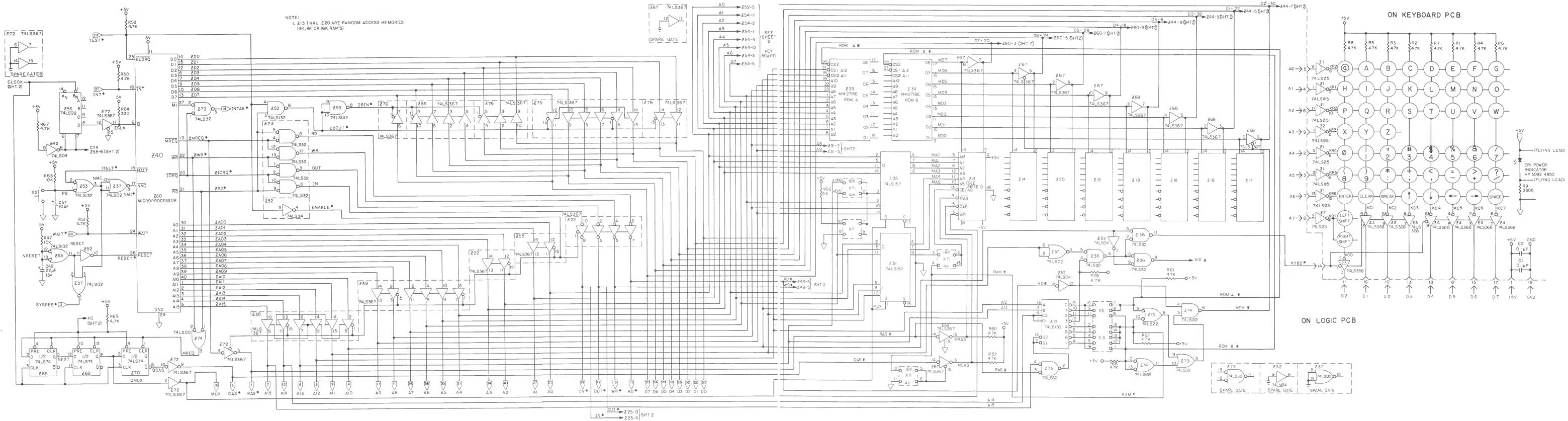

#### SYSTEM BLOCK DIAGRAM

The 80 integrated circuits contained in the TRS-80 can be broken down into about 10 major sections. Figure 1 shows these sections as they relate to other sections. The heart of the system is definitely the CPU (Central Processing Unit). You might consider the CPU as being a very dumb calculator circuit. It may be dumb, but it's a fast dummy. Most of the leads on the CPU are data lines and address lines. The CPU tells the address bus where the data it wants is located, and the data bus is a good place for the information to come back to the CPU. The address lines are outputs from the CPU. They never receive data or addresses from other sections. The data lines on the other hand can give or receive data.

#### ROM

The ROM (Read Only Memory) could be considered the brains, if the CPU has to be the heart, of the system. The ROM tells the CPU what to do, how to do it and where to put it after it's done. Without the ROM, the CPU would just sit there and oscillate. When power is first applied to the system, the CPU has just enough smarts to output an address to the ROM that locates the CPU's first instruction. The ROM shoots back the first instruction and then the two really start communicating. In less than a second, the CPU, under ROM supervision, performs all the house-keeping necessary to get the system alive and a "READY" flashes on the screen:

If the CPU misses that first piece of ROM data, then it may go bananas. It may tell the ROM that it is ready to load a tape so the ROM tells it how to do that. The tape recorder turns on. But since the CPU is now playing games in the video memory, who cares about the tape? The CPU operates at about 2 MHz; therefore, digital screw-ups seem instantaneous.

Remember that the CPU is the work horse and the ROM is the boss. The ROM tells the CPU how to do it, when to do it, and where to put it.

#### RAM

The next major section in Figure 1 is the RAM (Random Access Memory). This memory is where the CPU may place data it doesn't need until later. The RAM is also the place where the programs are kept for use. If you tell the computer to count to 10,000, then the CPU stores your instructions in the RAM. If you tell the computer to do it NOW, here is what happens:

The CPU tells the ROM someone wants in. The ROM tells the CPU to go to the keyboard and find out who. The CPU finds out, tells the ROM that it's <u>the</u> boss. The ROM tells the CPU to find out what he wants. The CPU tells the ROM that the boss wants US to RUN. The ROM tells the CPU to go to RAM and find out what the boss wants done. The CPU says the boss wants to count to 10,000. The ROM tells the CPU how to do it. After it's done, the ROM tells the CPU to find out what to do with it. The CPU informs the ROM that the 10,000 has got to go on the display and must be saved. The ROM tells the CPU how to put it on the display and then tells it to store the 10,000 somewhere in RAM; but it had better remember where it is. The CPU tells the ROM that the job is done. The ROM tells the CPU to monitor the keyboard in case the boss wants something else.

The CPU looks to the ROM for instructions. The CPU then follows the ROM's instructions and looks to the keyboard, then the RAM. In all cases, the CPU applies address locations to the ROM, RAM, and keyboard. The data lines are then checked for input data that corresponds to these address locations. In case of an output from CPU to RAM, the CPU selects the address, puts data on the data lines, then instructs the RAM to store the data that is on the data lines.

Notice that only the CPU communicates with all other sections. If the CPU is told by ROM to store something from ROM into RAM, the CPU can't make the RAM receive ROM data direct. Instead, the CPU takes the data from ROM and then sends it to RAM. The CPU must act as intermediary between the two. The reason for this is that the CPU is the only section that can address locations and pass data to all other sections.

#### KEYBOARD, VIDEO RAM, VIDEO PROCESSING

The keyboard section is not necessary as far as the CPU is concerned, but it is very necessary for the operator. The keyboard is our method of making known our instructions to the CPU. The opposite is true for the video RAM. In this case, the CPU wants to tell us it needs data or it may want to show us the result of a complex calculation. So, the request for more information or the result is stuffed into the video RAM. Anything in video RAM is automatically displayed on the monitor. The video processing section handles this. Data in the video RAM is in ASCII. Converting ASCII into the alphanumeric symbols we recognize is the job of the video processor. A ROM contains all of the dot patterns. The ASCII locates the character pattern, and the video processor sends it out to the terminal.

#### **VIDEO DIVIDER CHAIN**

Composite video going to a terminal is extremely complex. Aside from the video signal, there is the horizontal and vertical sync. These signals must be very stable and be outputted in the correct sequence. The CPU is busy enough as it is, so the video divider chain handles the TV work. It generates the sync signals and addresses the video RAM in a logical order so that the video processor can handle video data efficiently. Notice the block under the video RAM labeled MUX. This is short for Multiplexer. It acts somewhat like a multipole, multiposition switch. When the video divider chain is in control, the MUX is switched so that only addresses from the divider chain are directed to the video RAMS. The CPU may need to read or write data into the video RAM. If so, the MUX is switched so that the CPU has control over video RAM's address. After the CPU is finished, the addressing task is reassigned to the divider chain.

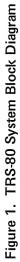

#### THE MEMORY MAP

Some customers call the Factory Customer Service Center and ask "Which output port is the display?" These customers are told that the TRS-80 does not use an output port for the display. They are told that the TRS-80 is memory-mapped. In a memory-mapped system an address will define and select all other subsections.

Figure 2 shows the memory map for a Level I TRS-80. From memory locations ØØØØ to ØFFF, the Level I ROMS are present. The keyboard is located from address 38ØØ to 38ØF. The video display is located from 3CØØ to 3FFF. The RAMs start at 400Ø and, depending on how much RAM is in the system, can extend down to address 7FFF.

NOTE: Map not drawn to scale

Figure 2. Level I Memory Map

As stated before, upon power-on, an address location is outputted by the CPU requesting information from the ROMs. Since the ROMs are located at addresses ØØØØ to ØFFF, the CPU will be outputting addresses in this area. If the CPU needs some kind of keyboard data, it will output addresses 380Ø through 38ØF and see if anything is in this "memory" location. If the CPU wants to show the programmer something on the display, all it has to do is address the video display section of the map and store data in these locations. Something to remember: the video display shows exactly what is in memory locations 3CØØ through 3FFF.

Notice memory locations 4000 to 41FF. At address 4000 RAM starts. But, part of the RAMs are used by Basic I as general housekeeping memory locations. Hence, the user accessible RAM actually starts at address 4200.

#### THEORY OF OPERATION

#### System Clock

The system clock is shown on Sheet 2 of the fold-out schematics in the Schematic Section. Y1 is a 10.6445 MHz, fundamental cut, crystal. It is in a series resonant circuit consisting of two inverters. Z42, pins 1 and 2, and 3 and 4, form two inverting amplifiers. Feedback between the inverters is supplied by C43, a 47 pF capacitor. R46 and R52 force the inverters used in the oscillator to operate in their linear region. The waveform at pin 5 of Z42 will resemble a sine wave at 10.6445 MHz. The oscillator should not be measured at this point, however, due to the loading effects test equipment would have at this node. Z42, pin 6, is the output of the oscillator buffer. Clock measurements may be made at this point. The output of the buffer is applied to three main sections: the CPU timing circuit, the video divider chain, and the video processing circuit.

#### **CPU** Timing

The Z8Ø microprocessor needs a single phase clock source for operation. The 10 MHz signal from system clock is applied to Z56, a standard ripple counter, which is used as a divide-by-6 counter. The resulting signal at Z56, pin 8, is a little over 1.774 MHz. The signal is applied to the input of buffer Z72, pin 12. Pin 11 of Z72 is attached to pin 6 of the Z80 microprocessor. R64 pulls up pin 11 of Z72, and insures a rapidly increasing rise time for the clock signal. Notice that pin 15 of Z72 is tied to ground. Since pin 15 is the enable input to this part of Z72, pin 12 and 11 will always be active. Notice also pins 7 and 6 of Z56. These two pins enable the clear function for the counter. When one or both of these pins is low, the counter operates normally. When high, the input forces the counter into its clear or reset state. Z42, pins 9 and 8, are used to disable counter Z56 during automatic testing at the factory. R67 pulls Z42's input to V<sub>CC</sub>, which causes pin 8 to stay at a logical low. During testing, pin 9 of Z42 may be pulled low, making pin 8 high, which disables and clears Z56. You might also find early Board levels (A Boards for example) where pins 6 and 7 of Z56 are tied directly to ground.

#### **Power-Up-Clear and System Reset**

As mentioned in the block diagram discussion, upon poweron the CPU accesses a known address in the ROM for instructions. The circuitry which causes the starting address output is shown just below the microprocessor clock divider. Z53 is a 2-input, quad NAND gate. (Note that Z53 is drawn like an inverted input OR gate.) When power is first applied to the system, C42 is at Ø volts. R47 is tied to V<sub>CC</sub> and starts charging C4 at a known rate. While C4 is charging, and before the voltage exceeds the logical 1 level for Z53, pin 11 outputs a high. This high is inverted by Z52, pins 11 and 1Ø, and a low is applied to pin 26 of Z4Ø.

A low at this input forces the microprocessor to output the starting address ØØØØ on its 16 address lines. When C42 charges up past about 1.4 volts, Z53, pin 11, goes low, which causes Z52, pin 10, to go high. The CPU is now out of its reset state, and will start executing instructions from the ROM, starting at address ØØØØ. Notice that the only time pin 26 of the CPU is ever low is a few milliseconds after power is applied. Once C42 charges up past the logical ONE level, pin 26 stays high until C42 is discharged when power is removed. Why is Z53, a NAND gate, drawn like an OR gate? Notice that pin 11 is high only when either of the inputs are low. The NOT circles at the input immediately tell you that this gate is looking for a signal that is low to cause an output that is high. Had the gate been drawn "correctly", then it would not have been so obvious that the output is active when high. This "functional" type of logical symbolization is used throughout the schematics.

Directly above the power-up circuit, there is a similar circuit. S2 is the reset switch located on the right side of the Board. Although there is a power-on-delay type circuit on the input of this network, it is not used as such. Notice that C57 is smaller than C42. Hence, in a power-up "race", C57 would charge up faster than C42. Assume that C57 is charged. Also assume that pin 2 of Z53 is high. This means that Z53, pin 3, will be low and Z37, pin 13, will be high. With pin 17 of the CPU held high, everybody is happy. If S2 is pressed, C57 will discharge through the switch. The resulting low is applied to pin 1 of Z53 and pin 3 goes high. Z37, pin 13, is then forced low. A low at pin 17 of the CPU forces the microprocessor to restart at address ØØ66. When S2 is released, R65 begins to charge C57 until a logical high is applied to pin 1 of Z53. At this time, pin 17 of the CPU goes back high and the CPU starts executing instructions from address ØØ66 in the ROMs.

S2 is used to get the microprocessor back on the right road when it is "lost". This switch forces the CPU toward a known address to enable it to get on the right track. An example of a lost CPU would be during a bad cassette load attempt. If a cassette is loading and suddenly there is missing information on the tape (caused by dirt or age), the recorder may never stop. S2 can then be pressed, which directs the CPU out of the cassette load routine and back into its ready mode.

The output at pin 18 of Z4Ø is called "Halt". In Level I BASIC, this output should never be low. It goes low only when a software halt instruction is encountered by Z4Ø. In theory, this instruction is not included in the ROMs. But you might find pin 18 held low because Z4Ø thought it was told to halt. It could be due to some data malfunction, or the CPU is lost and is playing around with display data instead of ROM data. In a case like this, S2 is not effective in bringing the CPU home, because Z53 is latched up. About all you can do is shut the computer down and try again.

Notice that Z53, pin 11 and pin 3, are also tied to Z37, pins 2 and 3. Z37, pin 1, is an output line labeled SYSRES\* (System Reset Not). It is normally-high and only goes low during power up (Z53, pin 11, causes this), or when S2 is pressed (Z53 pin 3, causes this). SYSRES\* is used by the expansion interface and is not used by the TRS-80 in BASIC I.

One last thing to mention about these two circuits: When you turn off power to the TRS-80 because of a lost CPU, wait at least 10 seconds before you reapply power. If you do not wait, C42 may not discharge all the way and the CPU may not go back to address 0000 during a restart. By waiting, C42 will discharge and upon power-up, the system will start at the correct ROM location.

# WAIT, INT\*, TEST

These three inputs to the CPU are pulled up to  $V_{CC}$  through resistors. Since they are active low, you may not have any use for them. But you should know what they are for.

The WAIT input, pin 24 of Z4Ø, will slow the CPU down if there are slow memories it must access. If this line goes low, the CPU will go into a wait status until it goes back high. Once high, the CPU continues with the operation. For example: Assume you have a memory system that takes 100 microseconds before addressed data can be guaranteed to be present at the output. When the memory logic sees that the CPU wants data, it will make the WAIT line low. At the end of 100 microseconds time, the logic will make the WAIT pin high, and the CPU will input the data.

The INT (Interrupt Request) is at pin 16 of Z4 $\emptyset$ . This input when low, will force the CPU into an interrupt request section of the memory. It would then perform some instruction associated with the interrupt. An example of this use would be as follows: Assume there was a door on the back of the TRS-80 that should always be closed. There was a switch connected to the door such that when opened, the switch contacts are shorted. The switch would be connected to ground and to pin 16 of Z4 $\emptyset$ . If the door were opened, the computer would stop what it was doing and print on the screen "Close Door." The CPU would be interrupted, and it would henpeck you until you closed that door! As you can see, pin 16 is tied to V<sub>CC</sub> through a resistor and is not used. It is, however, used with the TRS-80 Expansion Interface.

The TEST input may be quite useful in your troubleshooting. Pin 25 of Z4 $\emptyset$  is labeled BUSRQ (Bus Request). When this pin is brought low, it will force the data, the address and the control lines into the disabled or floating state. Although it is not used by the TRS-80 in normal operation, it is quite useful when someone wants to "shut down the CPU". We'll talk about this input when we discuss the Control Logic Group.

#### CPU ADDRESS LINES

There are system outputs of the microprocessor labeled A $\emptyset$  through A15 that start the address bus. Since these lines must go to ROM, RAM, the keyboard and the video RAM, they must be buffered for two reasons. First, the buffers must be able to supply the address bus with proper logical levels. The microprocessor cannot supply the current necessary to drive all of the sections connected to the address bus, and buffers are needed for current gain. Secondly, it may be necessary to switch off the address bus. For example, if an Expansion Interface is connected to the bus, it may be necessary to address RAM in the main unit for a data transfer. Therefore, there must be some method to take the CPU off the data bus. The buffers are tri-state devices. This means they will either act as buffers or as opened switches.

Z38, Z39 and part of Z22 and Z55 are the address line buffers. Notice that in Z38 and Z39 there are two sections of buffers. The first section contains four buffers and the second section contains only two buffers. Each section is controlled by a single pin. The first is controlled by pin 1 and the second by pin 15. When these control pins are at a logical low, the buffers are enabled and will operate normally. When the control pin is at a logical high, the buffers are disabled, and will show a high impedance from input to output. The signal that controls the address buffers is labeled "ENABLE\*" and is sourced at Z52, pin 4. Pin 3 is the input for control line inverter, Z52, and is tied to the TEST\* line. Notice that R58 keeps this line pulled high. Hence, the address buffers' control line will always be at a logical low; and therefore, operating as buffers. If TEST\* is shorted to ground, the address buffers will be disabled. This feature could be very useful in troubleshooting.

#### **CPU DATA BUS**

The data bus is buffered like the address bus, except for one area. Notice that there are only eight data lines at the CPU, labeled DØ through D7. But there are 16 buffers. Remember that the CPU must receive data as well as send data. The address lines are strictly CPU outputs, while the data lines are inputs and outputs. Therefore, there must be two sets of buffers for the data line. One set handles CPU output data while the other set takes care of the CPU input data.

The output data buffers consist of all of Z75 and one section of Z76. The input buffers consist of one section of Z55 and the last section of Z76. Notice that the input and output buffers are connected "head to toe". This could cause problems if both were on at the same time! The control inputs to the output buffers are all connected together on the line labeled DBOUT\*, and are in turn tied to Z53, pin 6. Likewise, the input buffers' controls are tied together on the line labeled DBIN\*, and are connected to Z53, pin 8. DBOUT\*, is tied to pins 9 and 10 of Z53, the gate which generates DBIN\*.

As you can see, Z53, pin 6, is the major source of input or output data control. If pin 6 is high, DBOUT\* is high and DBIN\* is low. Therefore, the input buffers are enabled and the output buffers are disabled. If Z53, pin 6, is low, DBOUT\* is low and DBIN\* is high. In this case, the output buffers are enabled and the input buffers are off.

Pin 4 of Z53 is tied to TEST\*. If TEST\* is grounded, not only will we disable the address buffers, but we will also cause pin 6 of Z53 to go high. Hence, the data output buffers will be off, robbing the CPU's control over the data lines. Since DBIN\* is now held low, the input data buffers would be active. But, this would not cause any problem since the address bus from the CPU has been disabled.

When TEST<sup>\*</sup> is left alone, it is held high. If pin 21 of the CPU (the Memory Read output) is high, Z53, pin 6, will be low. The low causes DBOUT<sup>\*</sup> to be low and DBIN<sup>\*</sup> to be high. Therefore, the CPU is outputting data; and the buffers are switched accordingly. When pin 21 of Z4Ø goes low, Z53, pin 6, will be high. We now have almost the same condition as if TEST<sup>\*</sup> went low. DBOUT<sup>\*</sup> is high and DBIN<sup>\*</sup> is low but the address buffers are still enabled. The data buffers are now ready for the CPU to accept data.

#### CPU CONTROL GROUP

OK, we now know how the CPU accesses the address bus. We know the data bus is used to gather data into the CPU or pass data out of the CPU. What we do not know at this point is how the CPU stores data in a memory or how it tells the ROM or RAM that it is ready to receive data. The CPU control group performs this task. These signals are: RD, WR, OUT, and IN.

#### RD (Read)

RD is Read control. This signal, when activated, will tell other sections that the CPU is ready to accept data. RD is generated at Z23, pin 6. Pin 5 is connected to pin 21 of Z4Ø, the RD (Read) output. Pin 4 of Z23 is tied to pin 19,  $\overline{\text{MREQ}}$  (Memory Request), of the CPU. Therefore, when pins 19 and 21 of Z4Ø go low at the same time, an RD output is generated. Notice the backward symbol for an OR gate. It's drawn like an AND gate. When we get  $\overline{\text{MREQ}}$  and  $\overline{\text{RD}}$ , then and only then will we get RD. We're looking for two lows on the input for a low output.

#### WR (Write)

WR is Write control. This signal, when activated, will tell other sections that the CPU is ready to write data into one of the memory locations. WR is generated at Z23, pin 11. Pin 12 of Z23 is connected to MREQ. Pin 13 of Z23 is tied to WR (Memory Write), which is pin 22 of Z4Ø. When we get a low at the MREQ output and a low at the WR output, then and only then will we get a low at WR.

#### OUT (Output)

OUT is Output control. This signal, when activated, will enable circuitry to perform the cassette save functions. It would also be used to control data movement from the TRS-80 to the Expansion Interface. OUT is generated at Z23, pin 3. Pin 1 of Z23 is tied to the WR output on the CPU. Pin 2 of Z23 is tied to IORQ (Input/Output Request) which is pin 20 of the CPU. When we get a low at WR and a low at IORQ, then and only then will we get a low at OUT.

#### IN (Input)

IN is Input control. This signal, when activated will enable circuitry to perform the cassette load function. It would also be used to control data movement from the Expansion Interface to the TRS-80. IN is generated at Z23, pin 8. Pin  $1\emptyset$  of Z23 is connected to IORQ. Pin 9 of Z23 is tied to RD. When we get a low at RD and a low at IORQ, then and only then will we get a low at IN.

#### CONTROL GROUP BUS

The Control Group must be buffered for use by the different sections. Also, the bus may need to be switched off at some time. Therefore, part of Z22 is used to buffer the Control Group. Tri-State control at pin 1 is tied to the address bus control, and ENABLE<sup>\*</sup> will affect the status of the address and the control group bus in the same manner.

#### ADDRESS DECODER

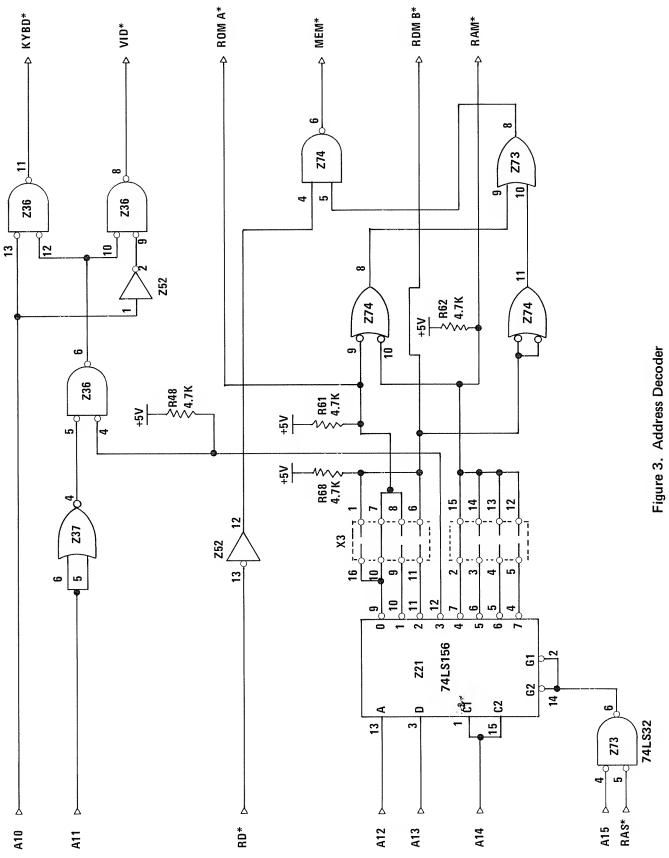

As shown in Figure 2, the TRS-80 is memory mapped. Therefore, the address Ø1AC (in HEX) is in the ROM part of the map. Address 38ØA is in the keyboard area and 3CAA accesses the video display RAMs. Since the data and address buses are connected in parallel to all the sections, there must be some method to determine which section is being accessed. A decoding network monitors the higher order address bits and selects which "memory" the CPU wants to use. The address decoder is so important to the operation of the system that it has been redrawn in Figure 3. Keep your schematic handy since there are signals shown in Figure 3 that need to be sourced or traced. The address decoder uses six bits. A1Ø through A15 are needed plus RD\* and RAS\* (RAM Address Select). A15 is the most significant bit of the address bus. Let's combine the six high order bits and add a couple more, so that we have two hex digits:

#### A15 A14 A13 A12 A11 A10 <u>A9 A8</u>

A12 through A15 form the most significant hex character. A8 through A11 form the next most significant hex character. A8 and A9 are the two bits we had to add to complete that last hex character. Now let's break down part of the memory map into hex and binary.

|                |   |   |   |   |   |   | 1 |                |              |  |

|----------------|---|---|---|---|---|---|---|----------------|--------------|--|

| From: Hex ØØØØ | Ø | Ø | Ø | Ø | Ø | Ø | Ø | Ø              |              |  |

| To: Hex ØFFF   | Ø | Ø | Ø | Ø | 1 | 1 | 1 | 1              | Level I ROMs |  |

| From: Hex 3800 | Ø | Ø | 1 | 1 | 1 | Ø | Ø | Ø              | Kaubaard     |  |

| To: Hex 380F   | Ø | Ø | 1 | 1 | 1 | Ø | Ø | Keyboard<br>ØØ |              |  |

| From: Hex 3CØØ | Ø | Ø | 1 | 1 | 1 | 1 | Ø | Ø              | Display PAMS |  |

| To: Hex 3FFF   | Ø | Ø | 1 | 1 | 1 | 1 | 1 | 1              | Display RAMS |  |

| From: Hex 4000 | Ø | 1 | Ø | Ø | Ø | Ø | Ø | Ø              | 4K RAM       |  |

| To: Hex 4FFF   | Ø | 1 | Ø | Ø | 1 | 1 | 1 | 1              | 41 11 AM     |  |

| From: Hex 4000 | Ø | 1 | Ø | Ø | Ø | Ø | Ø | Ø              | 16K RAM      |  |

| To: Hex 7FFF   | Ø | 1 | 1 | 1 | 1 | 1 | 1 | 1              | TOIL ITAM    |  |

A15 A14 A13 A12 A11 A10 A9 A8

Notice in the breakdown that we could use the two most significant digits of the hex code in the decoding scheme and handle the selection of all the memories. In the binary columns, you can see that instead of using two hex digits, which is eight binary lines, we can ignore two bits and use only six binary lines. A dotted line separates the two unused bits from the six that we'll use.

Looking at Figure 3, you'll see that bits A12, A13 and A14 are connected to Z21, a dual, 2-input to 4-line decoder/demultiplexer. The C1 and C2 inputs are connected in such a way as to make Z21 into a 3-input to 8-line decoder. The G1 and G2 inputs to Z21 are chip enables. As shown, when these inputs are at a logical  $\emptyset$ , Z21 is active. When high, Z21 is disabled and none of its eight outputs are low. The G enables are controlled by OR gate Z73, pins 4, 5, and 6. Pin 4 is tied to A15, the most significant bit of the address bus.

Notice in the memory map breakdown that A15 is always low when addressing the various memories. Z73, pin 5, is tied to RAS\* (Row Address Select). Go back to the big schematic, Sheet 1, and find MREQ at pin 19 of the CPU. As stated earlier, MREQ only goes low when the CPU needs or wants to output memory data. Follow pin 19 down to Z72, pin 4. This buffer sources RAS\* and it is the same signal as MREQ. Back to Figure 3. When A15 and RAS\* are low at the same time, a low will be outputted by Z73, pin 6. This low will enable Z21. When Z21 turns on, one of its outputs will go low, depending on the status of A12, A13 and A14. For example, if these three inputs are at logical zero, pin 9 will go low. If all three inputs are high, pin 4 will go low. You might consider A12 through A14 as supplying an octal address to Z21. Since there are eight states in an octal code, then there could be one of eight lines selected (Output  $\emptyset$ through Output 7).

We can sum up Z21's function quite simply: It decodes the most significant digit of the hex address. Using Z21 and the last two bits, A11 and A1 $\emptyset$ , we can define any one of the four "memories" available to the CPU in BASIC I.

#### ADDRESS DECODER PROGRAMMING

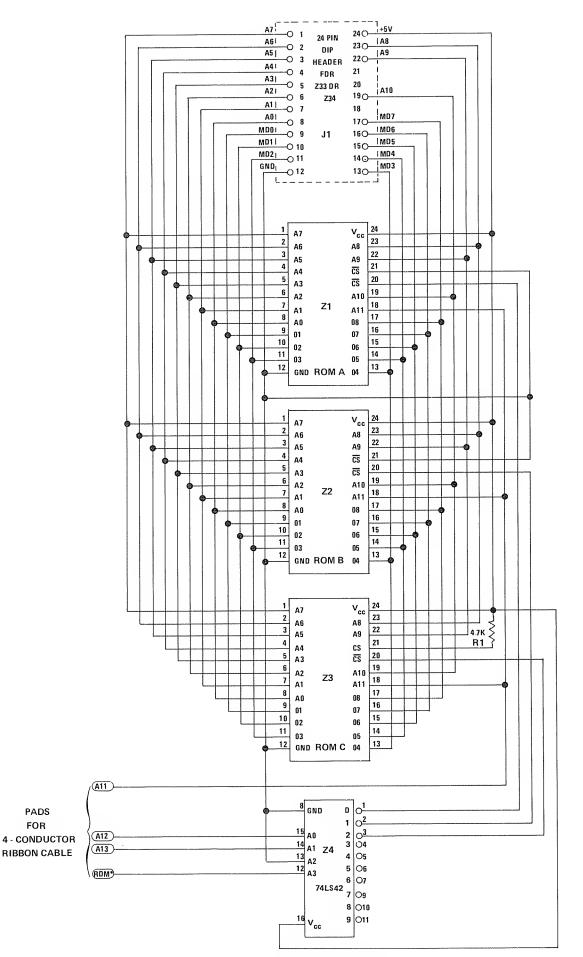

Attached to the outputs of Z21 is X3. X3 is called a "DIP shunt" and it is installed in the PCB position Z3. A DIP shunt is like a shorting bar array, except the bars may be broken. By breaking some bars and leaving others intact, the address decoder is programmed to reflect the amount of RAM or ROM the CPU has available for use. In Figure 3, X3 is shown with six broken shorting bars. We will use this configuration in our discussions.

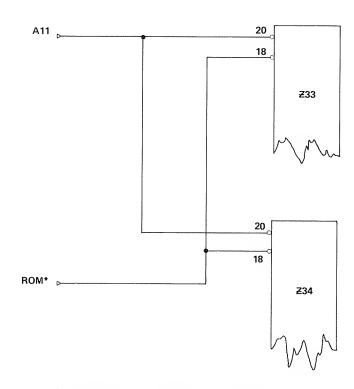

#### **ROM DECODING**

When the CPU needs instructions on how to perform a certain task, it must access ROM. ROM Decoding is performed as follows: The CPU needs a memory, so RAS\* will go low. The address for ROM starts with hex Ø, so A15, A14, A13, and A12 go low. Z21 becomes active due to the low at A15 and RAS\*. Pin 9 of Z21 goes low. Follow pin 9 through the shorted bar at X3 pins 10 and 7, past the pull-up resistor R61 and out to ROMA\*. If you find ROMA\* on the large schematic, you'll see it goes to ROM A, (Z33, pin 20.) This pin is the CS (Chip Select) and it is active low (as the inverting circle on pin 20 shows). Z33 turns on, which means that its output becomes active (Note: the ROM's outputs are tri-stateable like the buffers. When CS goes low, the ROM outputs will switch from a high impedance or off-state to an on-state. When on, the outputs will go low or high depending on the data in the ROM at the address specified.) We got the address applied to ROM A and we got ROMA\* to go low, so ROM A is turned on. But now we need to insure a data path is opened so that we can pass data from ROM to CPU. Notice in Figure 3, ROMA\* is also attached to pin 9 of NAND gate Z74. A low on pin 9 will cause a resulting high at pin 8. Z74, pin 8, is tied to Z73, pin 9. Z73, pin 8 passes a high to Z74, pin 5. Z74, pin 4, is tied to RD\*, part of the CPU control group. Since the CPU is trying to read data from ROMs, RD\* will be low. Pin 4 of Z74 will then be high, because  $RD^*$  is inverted by Z52, pins 13 and 12. OK, we know pins 4 and 5 of Z74 are high, so that makes pin 6 low. This low is MEM\*. If you find MEM\* on the big schematic, you will notice it controls the ROM/ RAM buffers. The outputs of the buffers are tied to the data bus. We now get ROM data onto the data bus. Has it got a way to get to the CPU? Yes, it does. Remember that RD is low because the CPU is in a Memory Read cycle. Since this is so, DBIN\* is low and DBOUT\* is high. The low at DBIN\* enables the CPU's input data buffers and ROM data is available for the CPU.

The keyboard is located from address 3800 to 380F. The keyboard is memory, so RAS\* will be low. A15 is low because we are generating address codes under 8000. Looking at our binary location for the keyboard, we find A14 low, A13 and A12 high. With this input combination, Z21 will be active and pin 12 will be low (Output 3). Pin 12 is tied to Z36, pin 4. According to the breakdown, A11 is high. Z37, pin 4, outputs a low to Z36, pin 5. The "incorrectly drawn" OR gate tells us we need both inputs low for a low output. We got it, so pin 6 of Z36 is also low. Pin 6 of Z36 is tied to pins 12 and 10 of Z36. Checking on the status of A10, we find it listed as being low during a keyboard address output. Since Z36, pins 12 and 13 are low, we'll get a low at pin 11. KYBD\* is generated at this pin.

Finding KYBD\* on the big schematic, you'll see it goes to the enable inputs of the data buffers for the keyboard. The lower order address lines are tied to one end of the keyboard matrix, while the other end of the matrix is tied to the data bus, through the buffers. If a key is pressed, an address line will be "shorted" to a data line. Assume for now that this scheme works. We'll analyze the keyboard later. The DBOUT\*, DBIN\* signals are switched the same way as if we had a ROM select. Therefore, keyboard data will get to the CPU's data bus for processing.

#### VIDEO DISPLAY RAM SELECT

In the binary breakdown for the memory map, you will notice that the binary out for the video RAM address is almost the same as the keyboard except for bit A1Ø. Z21, pin 12, will output a low to Z36, pin 4. Since A11 is still high, Z37, pin 4, will supply a low to pin 5 of Z36. Therefore, pin 6 of Z36 is low, just as if a keyboard was selected. Since A1Ø is now high, Z36, pin 11, is high and KYBD\* is not active. But Z36, pin 1Ø is low and so is pin 9 due to the effects of inverter Z52, pins 1 and 2. Hence, Z36, pin 8, goes low and we have caused VID\*, the Video RAM select, to become active. Assume for now that VID\* does select the video RAMS. We'll discuss what it does and how it does it later.

#### **4K RAM DECODER**

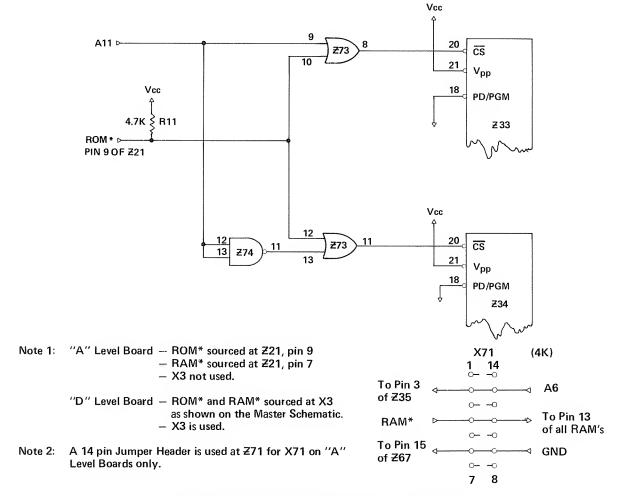

As shown on the memory map, the address which selects RAM extends from hex 4000 to 4FFF for 4K. The binary breakdown lists the states of A15 as a 0, of course. A14 is high and A13 and A12 are low. We are still accessing memory, so RAS\* is low. Hence, Z21 will be active and output 4 will be low (pin 7). DIP shunt X3 passes this low through pins 2 and 15, and it is applied to Z74, pin 10. It also is outputted by the decoder section as RAM\*. RAM\* will select the  $\overline{CS}$  pin on all of the RAMs, after it passes through DIP shunt X72. (It's shown on sheet 2 of the large schematic.)

The selection of the data bus for RAMs is handled the same way during a ROM-Read operation. MEM\* will go low because RD\* went low. But during a CPU data dump from CPU to RAM, MEM\* does not select the data bus buffers for the RAM. Instead of RD\* being active, WR\* is low. We don't need the ROM/RAM buffers because the RAM data inputs are on the output side of the buffers. Only during a ROM/RAM read operation do we need MEM\*.

Notice on X3 that we can program the system for 8K of RAM by leaving the shorting bar intact at pins 3 and 14, and at the 2 and 15 position. Not only would a 4000 address cause RAM\*, but a 5000 address would also enable RAM\*. If we had 12K of RAM, we would leave pins 4 and 13 shorted. For 16K, we short all pins we have mentioned; plus pins 5 and 12. RAM\* would now be active from addresses 4000 to 7FFF.

As you can see from the RAM discussion, we'll be shorting certain outputs of Z21 together. In most applications, using TTL, shorting output nodes is bad design practice. But there are some TTL devices that are called "open collector" types. These types of gates do not have an active pull-up on the output. Instead, the output transistors have "open collectors". It is the responsibility of external circuitry to pull them up. The "Open collectors" outputs may be tied together for a "wire OR" function.

Since Z21 is an open collector decoder, the output may be safely tied together. Notice resistors R48, R61, R62, and R68. These are the pull-up resistors for Z21. Something to remember about open collector outputs: You cannot tell if one of these outputs is working unless there is a pull-up resistor tied to that output. For example, if you placed an oscilloscope probe on pin 10 of Z21 as shown in Figure 3, you would not be able to tell if pin 10 goes low. If the system is working right, it shouldn't. But if it isn't working right and pin 10 is going low, how are you going to prove it? Pull it up with a resistor to +5 volts and see; that's the only way you can be sure.

#### SYSTEM RAM

According to the block diagram, system RAM is tied in parallel with the data bus and address bus just like ROM and the keyboard. The data input and output for RAM is straightforward enough; MEM\* controls the buffers. But the addressing scheme appears all screwed up. How can the CPU address a minimum of 4K of RAM using only seven address inputs? The answer to that very good question is multiplexing. The address from the CPU is multiplexed into the RAM in two 7-bit parts. The RAM's internal logic takes the two parts and brings them together to form one address scheme with 14 bits. One part of the addressing is called RAS\* (RAM Address Select); the other part is CAS\* (Column Address Select). Another signal, MUX (Multiplexer), controls the switching function. All three of these signals are generated near the CPU on Sheet 1 of the schematic section.

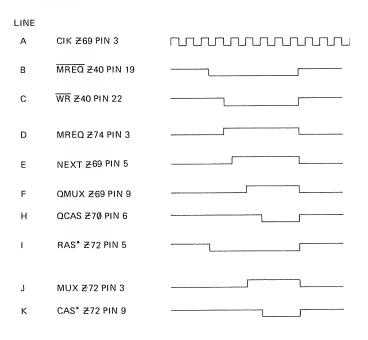

#### MUX, CAS\*, RAS\*

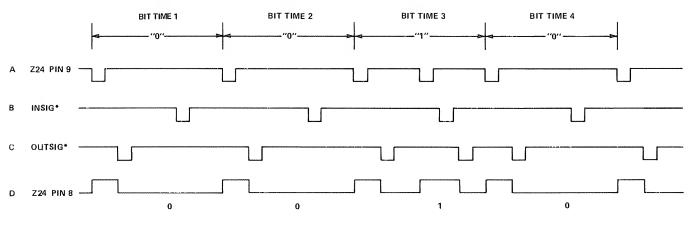

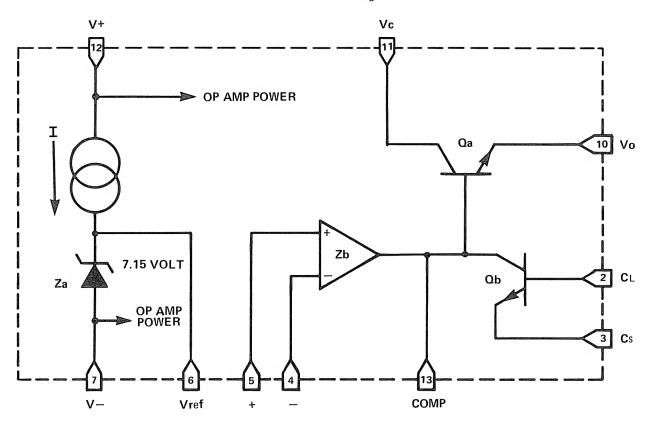

On Sheet 1, find pins 21 and 22 of the CPU. Follow the lines tied to these two pins down to NAND gate Z74. If we get a low at WR (Memory Write) or a low at RD (Memory Read), Z74, pin 3, will output a high (called MREQ, Memory Request). MREQ is tied to the clear inputs of Z69 and part of Z7Ø. These devices are D type flip-flops where the MUX\* and CAS\* signals are generated. Figure 4 shows a waveform chart for this circuit. Line A shows the master clock input to the flip-flops. Line B shows MREQ and Line C depicts the WR output from the CPU. Assume that the CPU wants to write data into RAM. As shown on line B, MREQ will go low. A short time later, WR will go low. Line D shows Z74, pin 3, going high at the same time as  $\overline{WR}$ went low. The flip-flops now have a logical high applied to the clear inputs. The flip-flops are free to operate, controlled by the clock waveform. On the next rising edge of the clock, Z69, pin 5, will output the logic level that was present at pin 2 the instant that pin 3 went high. Since pin 2 was high when pin 3 went high, pin 5 will go high. This high is shown on line E. Z69, pin 12, is now high; so on the next rising edge of the clock, pin 9 will go high. This is shown on line F. Z7Ø is ready to toggle. On the next rising edge of the clock, Z7Ø, pin 6, will go low (Q went high, so Q must go low). This is shown on line H of Figure 4. All three flip-flops have changed states since WR went low. The flip-flops will stay in this state so long as WR stays low. When WR does go high, the flip-flops will have a low applied to their clear inputs; and they will reset back to the clear condition.

Figure 4. Waveform Chart

11

Line I is the RAS<sup>\*</sup> output. As you can see, it is a direct function of MREQ from the CPU. Z72, pins 4 and 5, is RAS<sup>\*</sup>'s buffer. Line J, MUX is sourced at Z69, pin 9, through buffer Z72, pins 2 and 3. Line K, CAS<sup>\*</sup>, is buffered by Z72, pins 10 and 9, and is a function of QCAS, at Z70, pin 6.

Notice the following sequence of events: RAS\* goes low first. MUX then changes states. CAS\* then changes states one clock cycle later. First, we get RAM address select, then MUX, then we get Column Select. Hence, the first part of the address we give the RAMs will be the row address. We'll then flip the switch (multiplexer) and follow with the column address.

#### RAM ADDRESSING

In about the middle of sheet 1, on the left side of the RAM array, multiplexers Z35 and Z51 are shown. On the left side of Z35, we find the area where four address lines are coming in. One brace of four is labeled "O" and the other is labeled "1". Z51 is configured the same way except there are only three lines per brace. The Ø tells us that when the select pin is low, the multiplexer will be outputting data associated with these input lines. The "1" tells us the opposite is true. When the select pin on the multiplexer goes high, it will be outputting data associated with the "1" input address lines. The select input for both multiplexers is pin 1. Z35, therefore, operates somewhat like a 4-pole, double throw switch, where the select input (pin 1) is doing the switching. Z51 is used only as a 3-pole, double throw switch - one input/output is not used. The enable input to the multiplexer is pin 15. Since pin 15 is grounded on both IC's, the "switches" are always enabled.

#### **READING FROM RAM**

Assume the CPU needs RAM data. Let's follow the addressing and data paths the RAM will use. We'll use a 4K RAM example.

The CPU outputs a  $\overline{MREQ}$  and a  $\overline{RD}$ . The address decoder outputs MEM\* and RAM\*. MEM\* activates the RAM/ROM data buffers and RAM\* enables the chip select (CS) for the RAMs. At the same time, the multiplexer will load the address into the RAMs. RAS\* goes low. The MUX signal is low at this time, so AØ through A5 on the RAM receive the low order address. Notice that RAS\* is buffered by Z68, pins 14 and 13, and is applied to pin 4 of all the RAMs. The negative going signal at pin 4 will load the lower order address in the row section of each RAM. A short time later, MUX changes state; it goes high. The multiplexer, Z35 and Z51, now switch and the high order addresses are applied to the RAMs. CAS\* will now go low. CAS\* is applied to buffer Z67, pin 14. Pin 13 of Z67 passes CAS<sup>\*</sup> to pin 15 of all eight RAMs. On the negative transition of CAS\*, the high order addresses (A6 through A11) will be loaded in the column section of each RAM. The RAMs now have the entire address from the CPU. The RAM will now output data through the buffers and to the CPU.

#### WRITING TO RAM

The difference between a write operation and a read operation is exactly two signals. Address decoding and address multiplexing work the same way. During a data write, however, the CPU sends data to the RAMs. Hence, the ROM/ RAM buffers are not needed; and MEM\* will not go low. Instead of the CPU issuing a  $\overline{RD}$  command, it supplies a  $\overline{WR}$  instruction. WR\* is tied to all eight RAMs on pin 3. When this pin is low, data will be stored in RAM at the specified address. When this pin is high, the RAMs are in read cycle.

#### **REFRESHING THE RAMS**

The TRS-80 uses dynamic type RAM. A dynamic RAM differs slightly from a static RAM in data retention. A static RAM will retain data stored in it so long as power is applied to it. A dynamic RAM must be periodically addressed to ensure that it retains the data loaded into it. The periodic addressing is called refreshing. You might compare a dynamic RAM with an air-filled tire with a slow leak. Every once in a while, the tire must be shot a little air so it won't go flat. If we did not service that tire, it would finally become unusable. The same is true about dynamic RAM. If the system does not access the RAMs every so often, they will "forget" data.

The dynamic RAM in the TRS-80 uses an "RAS Only" type of refresh. In other words, when RAS<sup>\*</sup> goes low, the RAMs in the system will "refresh themselves" even though the RAM may not be in use at the time. As stated before, RAS<sup>\*</sup> is generated by the CPU at pin 19 ( $\overline{\text{MREQ}}$ ). Whenever  $\overline{\text{MREQ}}$  goes low, RAS<sup>\*</sup> goes low; and the RAMs will load the lower order address into the row section. The CPU may be looking at system ROM when MREQ goes low, but RAM will still receive RAS<sup>\*</sup> and hence be "refreshed."

Normally, you would not be too concerned about this aspect of the RAMs. But you need to be aware of the differences between a static RAM and a dynamic RAM. Remember: Dynamic RAM must be periodically addressed to enable it to retain data. In the TRS-80, the RAM should be refreshed once every two milliseconds.

#### RAM PROGRAMMING

You may have noticed X71 during the discussion of the RAM. X71 is a DIP shunt. It is used to program the size of memory in a system. Find pin 13 on the RAM. Following pin 13 down, you will see it is tied to two pins of DIP shunt X71. Pin 13 of the RAM is the CE (Chip Enable) or the A6 address input. In a 4K system, pins 4 and 13 of X71

are shunted. RAM\* is on pin 4 so RAM\* is used to select RAMs. But in a 16K system, 4 and 13 are opened and pins 3 and 14 of Z71 are shorted. Instead of RAM\*, we'll get address line A6 or A12 (depending on multiplexer status) going to pin 13 of the RAMs. There are other parts of X71 shown on the left side of the multiplexer, Z35 and Z51. Before troubleshooting a system, you will need to know the size of RAM the system uses. If X71 is "programmed" wrong, you may find yourself with RAM problems.

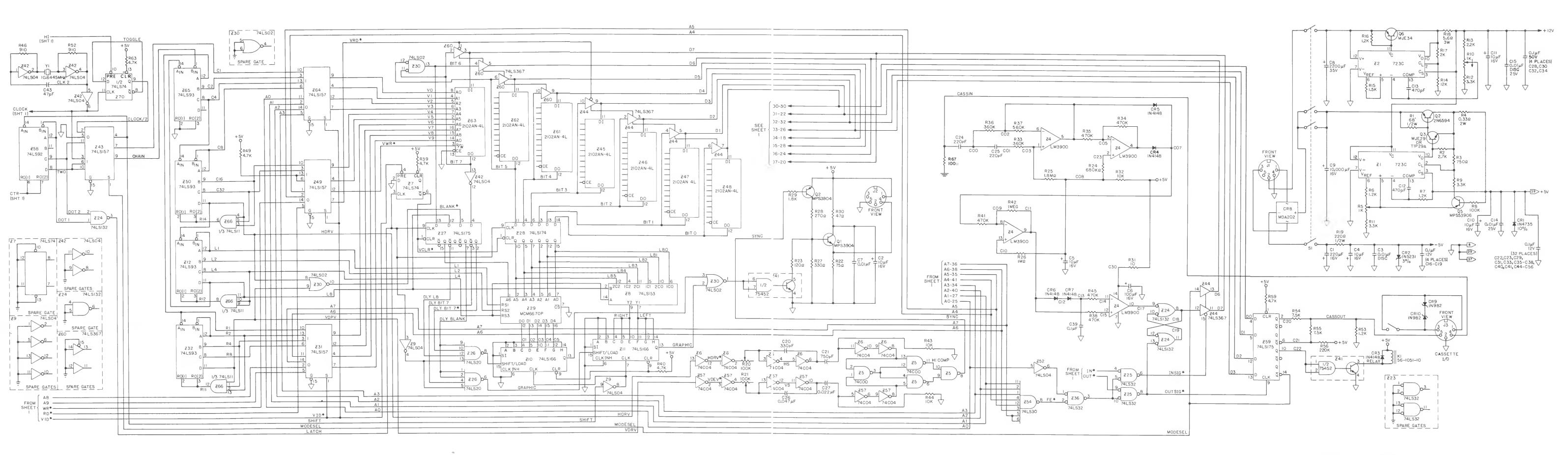

#### VIDEO DIVIDER CHAIN

The video divider chain supplies the video RAMs with addresses in a logical order for video processing. This chain also supplies the horizontal and vertical sync timing pulses so that the video processor can build the composite waveform for the display. Video RAM addresses, horizontal and vertical sync, and video processing timing are all direct functions of the master clock. Also included in the divider chain is the hardware necessary to generate 32 character line lengths. Although BASIC I can not access the 32 character format, BASIC II can.

#### **DIVIDER CHAIN – INPUT CONDITIONING**

If the TRS-80 did not have to change character line formats, the divider chain could have been tied directly into the master clock. But, the TRS-80 does have two formats for character lengths. In the most familiar format, the display has 16 character lines, each consisting of 64 characters. This means there are 10/24 character locations in video RAM the divider chain must access. In the other format, the characters appears twice as large. The display will show 16 character lines of 32 characters. The divider chain must access only 512 video RAM locations. Switching from one format to the other is the job of the input conditioning logic.

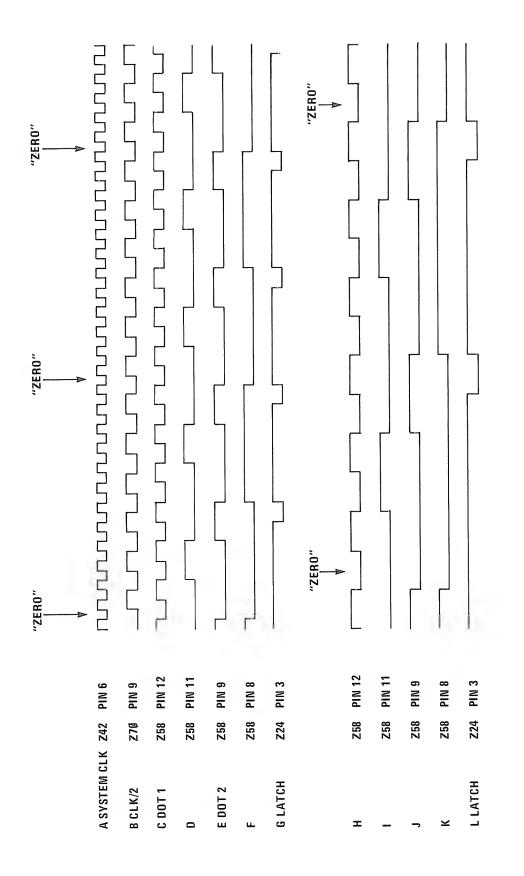

On sheet 2 of the schematic section, the master oscillator circuit is surrounded by a D flip-flop (Z70), a divide-by-12 counter (Z58) and a multiplexer (Z43). The D flip-flop is wired to perform a divide-by-two function. The multiplexer is wired such that we can route the master clock frequency, or the clock frequency divided by 2, from the flip-flop to the divide-by-12 counter. Since there are two character length formats, there must logically be two reference frequencies; one is half again as slow as the other. The master oscillator supplies the divide-by-12 counter with a reference frequency in a 64 character format. The D flip-flop supplies the counter with the reference frequency in a 32 character format.

The multiplexer is doing the selecting, so what is controlling it? Pin 1 of Z43 is a signal called MODESEL (Mode Select). When low, MODESEL forces Z43 to be switched into its 32 character position. When high, MODESEL forces Z43 to be switched into its 64 character position. Let's look at the 64 character mode first. Since MODESEL is high, pin 3 is "shorted" to pin 4 of Z43. Pins 6 and 10 are "shorted" to pins 7 and 9. (Remember: a multiplexer is an electronic equivalent of a multipole, double throw switch.) Figure 5 is a waveform chart for this circuit. At line A, the master clock is shown at the output of its buffer, Z42. Line B shows the action of D flip-flop during its divide-by-2 function. The buffered clock is applied to pin 3 of Z43. Since the multiplexer is switched into its "1" state, pins 3 and 4 are the same signal and counter Z58 receives the 10 MHz clock frequency at pin 14. Notice that flip-flop output Z70, pin 9, is tied to pin 2 of Z43. It is not performing any function at this time since the multiplexer is not switched into its "0" state.

The output of Z58 is shown at lines C, D, E, and F in Figure 4. The arrows in this figure points out the place where Z58's outputs are all zero. Notice that lines C through F do not count up to 11, then go back to zero using straight binary. Z58 starts fine:  $\emptyset \dots 1 \dots 2 \dots 3 \dots 4 \dots 5 \dots$  On the next clock, it goes from binary 5 to binary 8. From 8, it counts normally to binary 13; then on the next cycle, it goes back to binary zero.

Notice pins 6 and 7 of Z58. These inputs are used to clear the counter to zero. If you find CTR on sheet 1, you will see it comes from inverter Z42, pin 8, which controls the CPU CLK divider. Normally, CTR is held low. Only during automatic testing at the factory is CTR allowed to go high and clear Z58. You might find "A" and "D" Level Boards with Z58, pins 6 and 7, simply tied to ground.

Z58, pin 12, is labeled DOT 1. Z58, pin 9, is labeled DOT 2. DOTs 1 and 2 are "nanded" by Z24; and the resulting output is shown in Figure 5 at line G. This signal is called "LATCH" and is used in video processing.

Z43, pins 6 and 10, are tied together and are connected to Z58, pin 8. The resulting output is Z43, pins 7 and 9, will therefore be the same signal. Pin 9, labeled "CHAIN" is the divider chain's main source. Pin 7 of Z43 is labeled "C1" and is tied to pin 10 of Z64, one of the video RAM multiplexers. C1 will be used to address the video RAM's least significant bit.

In the 32 character format, Z43, pin 1, will be low. Therefore, pins 2, 5 and 11 will be ''shorted'' to pins 4, 7 and 9 respectively. (The electronic switch was flipped.) Now we have the frequency source from Z70, pin 9, tied to counter Z58. Pin 7 of Z43 is held low all the time; and pin 9 of Z58 is now used as the source labeled "CHAIN". In Figure 5, lines H through K show Z58's outputs. Remember: We are using line B in the Figure as the input to Z58 instead of line A. Notice that Z58 is now being used as a divide-by-6 counter. The output at pin 9 is now "CHAIN" instead of pin 8. Has the CHAIN frequency changed? No. In 64 64 character mode, we had the master clock, divided by 12, as the chain frequency. That is 10.6445 MHz divided by 12 = 887.041 KHz. In 32 character mode, we had 1/2 master clock divided by 6, as the chain. 10.6445 MHz

divided by 6 divided by 2 = 887.041 KHz. What did change? Two signals changed. "LATCH" is sourced at Z24, pin 3. In 64 character format, the latch pulse was only one clock cycle (Master Clock) wide, having a period of 6 clock cycles. In 32 character mode, the pulsewidth has doubled to 2 clock cycles and its period is now 12 clock cycles. The other signal that changed was C1. Sourced at Z43, pin 7, it was a square wave at the same rate as the chain signal; but in 32 character mode, it is held low all the time. The signals that changed are very important to the video processor section. The first, LATCH, is used to delay a character between RAM and the character generator. The second signal, C1, determines if the RAM has 10/24 or 512 useable addresses.

#### **DIVIDER CHAIN**

The divider chain circuit of Z65, Z50, Z12 and Z32 consists of four bit, ripple counters. They have a maximum count of 16, but external circuitry may modify this maximum.

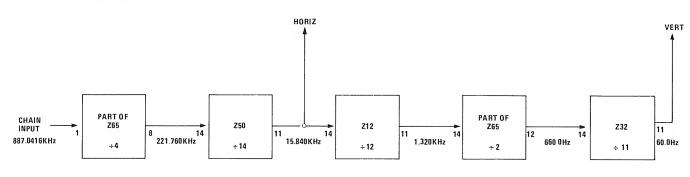

Figure 6 shows a simplified block diagram of the counter chain. Refer to figure 6 and to Sheet 2 during our discussion of the counter chain.

Z65 is a binary counter that is split into two parts. The chain input from the conditioning logic is applied to pin 1 of Z65. The B and C outputs are used for video RAM addressing, and the output of Z65 at pin 8 is applied to the next counter in the chain. This part of Z65 divides the chain frequency by 4. Since the chain is 887.0461 KHz, the output of Z65, pin 8, is 221.760 KHz. The other part of Z65 will be used later.

The next counter in the chain is Z50. The input is on pin 14 and the divided frequency is at pin 11. This device is externally modified to divide the input frequency by 14. Z50 counts up normally to a binary value of 13. Hence the counter's outputs are as follows:

| Pin 12 | (Output A) | =  | 1 |

|--------|------------|----|---|

| Pin 9  | (Output B) | =  | Ø |

| Pin 8  | (Output C) | == | 1 |

| Pin 11 | (Output D) | == | 1 |

Figure 6. Divider Chain Block Diagram

Upon the next negative transmission of the clock pulse, outputs would look as follows:

| Output A | =  | Ø |

|----------|----|---|

| Output B | == | 1 |

| Output C | -  | 1 |

| Output D | =  | 1 |

which is equal to 14. But notice AND gate Z66, pins 3, 4, and 5. These pins are tied to outputs B, C, and D. The output of the AND gates pin 6, will go high and clear Z50 back to zero. This clear pulse is extremely rapid – about 50 nanoseconds! The binary count of 14 would therefore be almost invisible to a standard oscilloscope and so would the clear pulse to pins 2 and 3. The time that Z50 is actually reading binary 14 is so short that we can ignore it. Therefore, Z50 will count from 0 to 13 and will then reset back to 0. Since 221.760 KHz is put into Z50, the output at pin 11 will be 15.840 KHz. This frequency will be used by the sync generator circuits to produce horizontal sync. The next divider is Z12. It is wired to perform a division by 12. It counts up normally until the outputs enable AND gate Z66, pins 9, 10, and 11. This happens at the twelfth falling edge of the clock. Z66, pin 8, will then go high and clear Z12 back to zero. Once again, this clear pulse would be very hard to observe using an oscilloscope. Hence we can ignore this count and consider Z12 as a divide-by-12 counter instead of a divide by 13 counter! If 15.840 KHz is applied to Z12, pin 14, then the output at pin 11 will be 1.32 KHz.

The next divider is part of Z65. On Sheet 2, follow pin 11 of Z12 up to Z65, pin 14. The output is at pin 12. Follow it back down to Z32, pin 14. This part of Z65 divides the 1.32 KHz input by two; therefore, the frequency at pin 14 of Z32 will be 660.0 Hz.

Z32 is the last counter in the chain. It divides the 660 Hz input by 11, producing 60 Hz. Once again, part of Z66 is used to modify the count. When the outputs of Z32 equal

binary 11, Z66 will output a very narrow pulse which clears Z32 back to zero. The 60 Hz at pin 11 is used by the sync generator circuits to produce the vertical sync for the monitor.

#### VIDEO RAM ADDRESSING <sup>-</sup>

During our discussion of the system block diagram, you noticed that the video RAMs must be addressed from two sections. The CPU must address video RAMs to read or write data from or to specific locations. The divider chain must also address video RAM so that data contained in memory can be processed and displayed on the screen. The video RAMs are addressed either by the CPU or by the divider chain through the use of three multiplexers.

Z64, Z49 and Z31 are the three multiplexers used for video RAM addressing. From the divider chain, there are 10 address lines that will be used to address video RAM. The chain conditioning logic supplies one address - C1. Z65 supplies three addresses - R1, C2 and C4, Z50 supplies three addresses - C8, C16 and C32. Z32 supplies the rest -R2, R4 and R8. Imagine an array of rectangles; 16 rectangles vertically and 64 rectangles horizontally. You would have a total of 1024 rectangles. You could specify any one rectangle by saying, "Starting at the top left hand corner, go down four rows and go to the right 18 columns." The 16 rows could be assigned a binary number from  $\emptyset$  to 15. The 64 columns could be assigned a binary number from  $\emptyset$ to 63. Rectangle  $\emptyset - \emptyset$  would be in the upper left hand corner of the array. Rectangle 15-63 would be in the lower right hand corner. Four bits of binary information would therefore specify any one of the 16 rows. It takes six bits of binary data to specify any one of the 64 columns. This is exactly the addressing format used by the counter chain. C1, C2, C4, C8, C16 and C32 specify any column. R1, R2, R4 and R8 specify a row. The row/column addressing format is very useful in troubleshooting video problems in the TRS-80.

The column and row address outputs from the divider chain are applied to the "1" inputs of the multiplexer. Part of the CPU's address bus is tied to the "Ø" input of the multiplexer. The outputs of the multiplexer are tied to the video RAMs or logic around them. We've got inputs and outputs; how about control? Do you remember the signal VID\* that we generated back in the address decoding discussion? We said VID\* will select the video RAMs. Notice that pin 1 of the 3 multiplexers is tied to VID\*. When the CPU wants control over the video RAM, the address decoder recognizes the video RAM address and causes VID\* to go low. When VID<sup>\*</sup> is low, the multiplexer switches the " $\emptyset$ " inputs over to the multiplexer outputs. The counter chain addresses are switched out of the circuit, and the CPU has control over video RAM. When VID\* goes back high, the CPU is switched out and the counter chain takes over. Most of the time, the counter chain is in control of video RAM. The CPU only takes charge when it needs to. You can see on the display screen when the CPU robs the counter chain of

16

video RAM control. Ever notice black streaks all over the screen while graphics are being drawn? These streaks are the result of the counter chain losing control over video RAM.

Aside from chain and CPU address, there are inputs to the multiplexer we have not yet mentioned. The first of these inputs is the resistor at pins 13 and 6 of Z49. These two inputs, which are not needed in the counter chain's control over video RAM, are pulled up to 5 volts by R49. Output pins 12 and 7 correspond to the inputs at pins 13 and 6. When the chain has control over video RAM, pins 12 and 7 output a steady state high. Pin 12 goes to the R/ $\overline{W}$  (Read/ $\overline{Write}$ ) control of all the RAMs. Since the counter chain never stores data in RAM at the address it specifies, pin 12 should be high when the chain is in control. Pin 7 of Z49 goes to the video RAM data buffer. When the chain is in control, the RAM data bus should be disabled. A high on VRD<sup>\*</sup> (Video Read) guarantees this bus will be off.

We also find WR<sup>\*</sup> and RD<sup>\*</sup> tied to pins 14 and 5 of Z49. When the CPU takes charge of the video RAMs, multiplexer output at pin 12 becomes VWR<sup>\*</sup> (Video Write). The CPU can store data into the video RAMs by causing VWR<sup>\*</sup> to go low. If the CPU wants to read data from video RAMs, RD<sup>\*</sup> can pass through Z49 and activate VRD<sup>\*</sup>. A low here will open data buffers Z6Ø and Z44. Addressed video RAM data is then placed on the data bus. The CPU can process this data like any other data.

#### ALPHANUMERIC FORMAT

The CRT (Cathode Ray Tube) in the display will be scanned twice per second. The electronic beam in the CRT travels from top to bottom of the screen and left to right. Each screen or frame consists of 264 scan lines. 192 scan lines are used in the "picture". 72 lines are used during vertical interval and as upper and lower boundaries. Nothing is ever "written" or visible within these 72 lines. There are 1024 character locations per screen (or 512, depending on status of MODESEL). Each character line consists of 64 characters (or 32, depending on the status of MODESEL). There are 16 character lines. Each character line consists of 12 scan lines. An alphanumeric character uses seven scan lines while there are five blank scan lines between character lines. We'll worry about graphics formatting later.

Part of Z65 and Z50 specify the column address. Z32 specifies the row (or character line). Z12 specifies the scan line in any character line. The outputs from Z12 are labeled L1, L2, L4 and L8. These four lines are not used in video RAM addressing because we already stated a row and column address will specify any one of the 10/24 rectangles in our rectangle array. Z12's outputs are used in the video processing. L1, L2, and L4 will enable the character generator to output correct data for any character since it knows where the CRT's electron beam is scanning. L8 is used by the video processor to blank (turn off) the five lines between character lines.

Notice NOR gate Z30, pins 8 and 9. These pins enable Z30's output to produce a signal called BLANK<sup>\*</sup>. BLANK<sup>\*</sup> is used by the video processor to give the 72 scan line blanking for the upper and lower boundaries. It also defines the blank boundaries on the left and right of the screen.

#### VIDEO RAMS

The video RAMs are static and hence do not need refreshing. The data bus is wired in the same way as system RAMs, but with a different enable signal. One interesting point to note: There are seven RAMs. Six are used for ASCII storage, and the seventh is used as a graphic/alphanumeric definition bit. There are eight data lines. Notice the line labeled Bit 6. It is sourced by NOR gate Z3Ø at pin 13. If Bit 5 (Z62, pin 12) and Bit 7 (Z63, pin 12) are low, then Bit 6 will be high. Z3Ø is a sneaky way of squeezing a seventh ASCII bit out of six RAMs.

Aside from the data bus, there is another RAM output for data. The video processor needs video data for generation of the alphanumeric and graphic symbols. And this section will be discussed next.

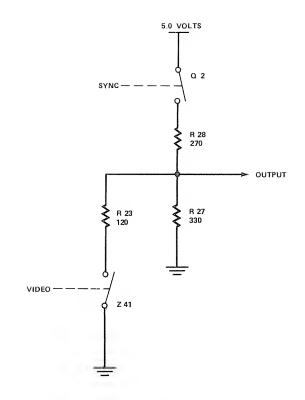

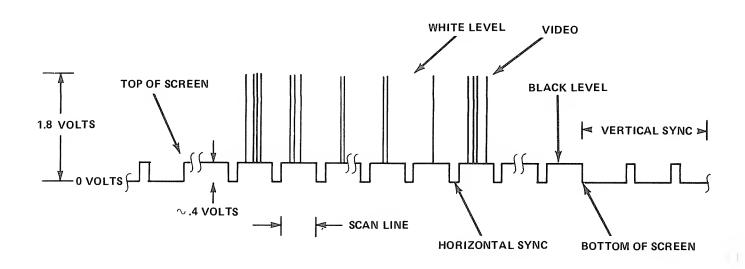

#### VIDEO PROCESSING

Video Processing consists of five subsections. They are: data latch, character/graphic generator, shift register, sync generator, and video mixing/output driver. The data latch temporarily stores an ASCII or graphic word from video RAM. The latch will retain the byte for processing so that the RAM is free to search out the next byte. The character generator is a ROM that is addressed by the data latch and the scan line signals. This ROM contains the alphanumeric format that makes up all the characters. The graphic generator is not a ROM, but a 4-line-to-1-line data multiplexer. It operates somewhat like a "bit steering" circuit. It steers an ASCII word into a graphic's symbol. The shift register accepts data from the character generator (or the graphic's generator) and converts parallel dot data into serial dot data. Meanwhile, the sync generator circuits have been accepting timing signals from the divider chain. The sync circuits shape up the horizontal and vertical pulses, serrate the vertical interval and sends it all out to video mixing in serial format. In the video mixing section, the serial dot video and the serial sync are brought together. The resulting composite video signal is then "fine tuned" in amplitude and dot-to-sync ratio, and then buffered for a 75 ohm output cable. The signal leaves the TRS-80 and is applied to the display. In the display, the signal is torn apart into its separate components; and you have a readable image on the screen.

#### DATA LATCH

The data latch consists of Z28 for the ASCII and Z27 for the graphic bit and blanking signals. The inputs of Z28 come from the six video RAMs. The outputs of Z28 go to

Z29, the alphanumeric character generator and to Z8, the graphics generator. The inputs which control Z28 are on pin 9 (latch) and pin 1 (VCLR\*). The latch signal at pin 9 is a pulse train developed by the divider chain-input conditioning logic. This signal goes low every six dot cycles (see Figure 5 for latch timing). On the rising edge of latch (low to high transaction), ASCII data in RAM is transferred to the outputs and temporarily stored by Z28. RAM data at the input to Z28 may now change, and the RAM has time to search for the next ASCII character. (RAM, any RAM, has a parameter called "Access time". This is the time it takes for the data output to reflect a change after an address change. For example, assume a RAM output is high. The address of the RAM is changed to a new location where a "Ø" data bit is stored. Even though the RAM is now addressing the low cell, the output still reads the previous high. Only after a short length of time - in the nanoseconds - will the output change from a high to a low.) At the same time Z28 stored the ASCII word, the divider chain changed video RAM addresses. The RAM is now "looking" for the next ASCII word. It has exactly six dot times (about 560 nanoseconds in 65 character format) to find it before the latch is commanded to store the next word.

Z27 is a smaller latch that operates in the exact same manner as Z28. But instead of ASCII, it handles the graphic bit and blanking data. Pin 4 is tied to the inverted output bit from Z63, the graphic RAM. Pin 5 of Z27 has signal BLANK\* tied to it. L8 is tied to pin 12 and our "sneaky" bit, bit 6, is tied to pin 13 of Z27. All of these signals are latched into Z27 at the same time as the ASCII word is latched into Z28.

Each input to Z27 has a different function. The graphic bit to pin 4 of Z27 will determine if the ASCII word contained inZ28 is an alphanumeric character or is a graphic word. Pin 5 of Z27, is signal BLANK\*. This signal comes from Z3Ø, pin 10, and controls the upper, lower, left and right boundaries of the video display. When BLANK\* is high, the CRT's electronic beam is allowed to draw on the screen. When BLANK\* is low, the beam is in a boundary area so it prevents the beam from drawing anything. L8 is connected to pin 12 of Z27. L8 acts somewhat like BLANK\*. L8, remember, specifies where the electron beam is located in any character line. When low, L8 allows the beam to output alphanumeric dot data. When high, L8 shuts off the beam because it is now scanning one of the five scan lines between character lines. The last piece of data comes into Z27 at pin 13. Sourced at Z3Ø, pin 13, this is the "sneaky bit" that is derived from data contained in RAMs Z63 and Z62. This is the only bit at Z27 which could be considered part of the ASCII word. The output is applied to character generator Z29, at pin 1.

Notice pin 1 of both data latches. This input, when low, will force the latches to their clear state (zero at the outputs). This signal is called VCLR<sup>\*</sup> (Video Clear) and is

sourced by D flip-flop Z7, at pin 6. The flip-flop disables the data latches during a CPU interruption of video RAM. Notice pin 4 of Z7. It is tied to VID\*. When VID\* goes low, Z7, pin 6, will go low. The low at pin 6 will clear the data latches. (This is what generates the black streaks we discussed in the video RAM addressing section.) When the CPU has finished with video RAM, pin 4 of Z7 goes back high. The next time data is to be latched into Z27 and Z28, Z7 will toggle back to its normal reset state and allow the data latches to operate. If Z7 was not used, we might see characters that appear ripped apart on the screen. For example, assume the CRT was drawing a character when the CPU took command of video RAM. After the CPU finished, the video processing circuit may still see the ASCII code that was in the latch at the time the CPU suddenly jumped in. The video circuit would try to redraw the character on the screen. We would then either see the character twice; or half of it would be over there, and the other half would be here! Clearing out the data latch insures us that the video processor does not get confused.

#### CHARACTER GENERATOR

Each character consists of a dot matrix. The matrix is five dots wide by seven dots deep. There is one dot between any two adjacent characters that are never turned on. We have five dots, a space, five more dots, a space, etc. Vertical spacing between adjacent data is determined by the frequency of the dot clock. (In the TRS-80, the dot clock signal is labeled SHIFT.) The dot clock is oscillator frequency, in 64 character format, and 1/2 oscillator frequency, in 32 character format. Horizontal spacing between adjacent dots is a function of scan frequency. In other words, each row of dots is aligned along the electron beam's path across the CRT. There are seven rows of character dots and five rows of blanks.

Since each character consists of a pattern of dots, there must be some method to determine which dot should be on and which dot should be off to form any one character. The character generator controls the dot patterns on the screen.

Z29 is the character generator. The seven bit ASCII word, stored in the data latch, is applied to Z29's ASCII inputs, pins 1 through 7. The ASCII addresses a certain area in Z29. You might consider the ASCII inputs to be the higher seven bits of an address. The lower part of the address is inputted at pins 8, 10 and 11. This three bit input selects the row position of the addressed dot pattern. Z29 outputs five dots at one time. Since each character consists of seven rows of five dots, the character generator must output seven separate times just to build one character. Here is how a typical character line is written: Assume an ASCII word is in the latch. The electron beam is on the first scan line of the character. Hence, pins 8, 10 and 11 have a binary "O" applied to them. Z29 outputs the first dot pattern for that particular ASCII character. The next ASCII character is applied to Z29. It outputs the first five

dots for that character. This process goes on until the beam has scanned the entire width of the screen. If we could stop action at this point, all you would have would be a line of dots. On the second scan line, the data at pins 8, 10 and 11 is incremented to read binary "1" (ØØ1). The RAM is now prepared to read the second row of dots. The first ASCII character is applied, and it will output the second row of dots for that character. The second ASCII word comes in, and the second row of dots go out. This process continues until all 64 characters have had the second row outputted under the first row of dots. The line counter increments and we apply the first ASCII word once more. We paint a row of dots, increment the line counter and paint another row. Any character in a line is accessed at least seven times. Once the line counter has gone past the seventh count, all the dots make sense; and we will recognize the dot patterns as characters. After the seven dot scans are outputted, the electron beam is turned off; and five rows of blank dots are outputted. We would now be ready to output the first row of dot patterns for the second character line.

The dot output appears slow-reading about it. But ASCII is being shot into the character generator at about a 1.77 MHz rate. The CRT and the retention of the eye make these characters seem like they are outputted whole.

#### **GRAPHICS GENERATOR**

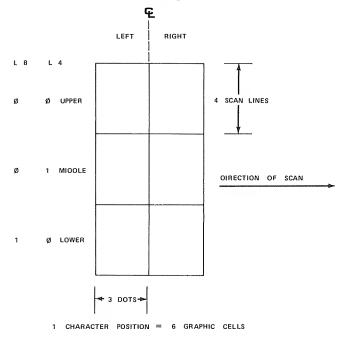

Do you remember the rectangle array we discussed in the divider chain section? Well, we are back to the rectangles. As stated earlier, there are 10/24 character locations in video RAM. If we divide each large rectangle into six smaller rectangles, we will have the basic graphics cell (Figure 7 shows a divided rectangle). This cell is the smallest piece of graphic information that can be displayed on the screen. Each cell is four scan lines long and three "dots" wide.

Z8 is the graphics generator. Actually, Z8 does not generate anything. Rather, it steers the ASCII addresses around to simulate a graphics generator. The input to Z8 is ASCII from data latch Z28, and the higher order line address from Z12, L4 and L8. L4 and L8 can represent any four numbers from  $\emptyset$  to 3. But since Z12 never goes to binary 12 (except for so short a time we can ignore it), we will only be looking for a binary number from  $\emptyset$  to 3. L8 and L4 are used to specify the vertical address of the six graphic cells. There are three vertical addresses:  $\emptyset\emptyset$  defines the uppermost pair of cells,  $\emptyset$ 1 defines the middle pair of cells, 1 $\emptyset$  defines the lower pair. This is also shown in Figure 3.

The ASCII word, labeled LBØ through LB5, determines if the graphics cell is ON (high) or OFF (low). The position of one of these inputs to Z8 determines which side of the center line the cell is located. An input at pin 6 of Z8 specifies a left hand graphic cell. Input at pin 10 of Z8 specifies a right hand graphics cell. Pin 5, left; pin 11, right; pin 4, left; pin 12, right. For example: Assume LB2 is high and all other LB inputs to Z8 are low. LB2 comes into Z8 at pin 5. This pin is associated with a graphic cell location on the left of the character position. Therefore, depending on the status of L8 and L4, LB2 will turn on (light) one of the graphic cells on the left of center line. If L3 and L4 are at logical  $\emptyset\emptyset$ , the upper left cell is turned on. If L3 and L4

As you can see, Z8's function as a graphics generator is to steer the ASCII bits around the character rectangle. The vertical position of the graphics in the cell is determined by the status of L8 and L4. The two outputs from Z8 are labeled "left" and "right". This "dot" information is applied to the graphics shift register. It is in shift register logic that data from RAM Z63 determines if graphics or alphanumerics will be written in any one character rectangle.

#### ALPHANUMERIC/GRAPHIC SHIFT REGISTER

Z10 is the alphanumeric shift register and Z11 is the graphic register. Both devices receive parallel data from their respective generators. The parallel dot data is loaded into the registers and the dot clock (labeled SHIFT) will march the dots out, one behind the other, to the video Mixer. We will discuss the alphanumeric shift register first.

There are a few restrictions when the alphanumeric shift register may serialize dot data and when it shouldn't. First, the data must be alphanumeric and not graphic. Second, the electron beam must be on one of the seven scan lines that are reserved for dot data and not on one of the five lines that are blanked (held off) between character lines. Third, the electron beam must be on one of the 192 scan lines that define the video portion of the screen. (not in boundary space — upper, lower, left or right). Once all three restrictions are met, the dot data is parallel loaded into the register. NAND gate Z26 insures all conditions are met before data is stored in  $Z1\emptyset$ .

Delay bit  $7^*$  is sourced from latch Z27, pin 2, and applied to pin 10 of Z26. When this input is high, data in Z63 is low, which defines an alphanumeric character.

Delay L8 is sourced at Z27, pin 11, and is connected to Z26, pin 12. When this input is high, the beam is scanning in a character line and not between character lines.

Delay BLANK is sourced at pin 7 of latch Z27 and is tied to pin 9 of Z26. When this input is high, the electron beam is in the video portion of the screen and is not located near a sync pulse or in some boundary region.

All three restrictions have then been met. Pin 13 of Z26 is tied to the inverted signal, LATCH. When pin 13 of Z26 goes high, the dot load process will be activated by a low on Z26, pin 8. Upon the next clock pulse at pin 7 of Z10, dot data will be loaded into the shift register. After LATCH goes back high (one dot time after going low), the shift register starts clocking dot data out at pin 13 in a serial stream (when LATCH goes high, pin 13 of Z26 goes low causing pin 8 to go high). Each time LATCH goes high, it forces ASCII and conditional data to be stored in Z27 and Z28. During this time, Z10 will not be shifting dots out at pin 13. Z10 only shifts data out when pin 15 is high. When low, pin 15 forces Z10 to load data from the character generator.

Notice the unused inputs to Z1Ø. Pin 9, the clear input, is pulled up, via R4Ø, to V<sub>CC</sub>. When this pin is low (due to a short), you would have a blank screen. Pins 14, 3, 2, 1 and 6 are tied to ground. Pin 14 gives you that blank dot between adjacent characters. Pins 2 and 3 are not used, but are register inputs like pin 4 or 5. Pin 1 is for serial data input and pin 6 inhibits the clock input. They are not necessary in this application.

The graphics shift register is Z11. Operation is almost the same as Z10, except for the condition that must be met for use. The graphics conditions are as follows: First, Z63 must specify a graphics character instead of an alphanumeric character. Second, the electron beam must be in the video region of the screen. There are only two conditions restricting graphics. Since a character rectangle ends where another starts, there is no inter-character line blanking. If you turn on all of the graphic cells, you would have a full, large square with no holes and boundaries surrounding the square. Once all of the restrictions are met, graphic dot data may be loaded into Z11 for shifting to the video mixer. The other NAND gate in Z26 is used as the graphics load enable.

The inverse of delay bit 7\* (DLY bit 7) is sourced at Z27, pin 3. It is applied to Z26, pin 4. When high, this input tells Z26 that Z63 does indeed contain a "1" which defines a graphic code.

Delay Blank (DLY BLANK) is tied to Z26, pins 1 and 2. When high, this input tells Z26 that the electron beam is indeed in the video portion of the screen.

Once all conditions are met and LATCH goes low, Z26 will go low. Just like Z1 $\emptyset$ , Z11 will load dot data; and when pin 15 goes back high, the shift process will start. The six graphic dots are shifted out of pin 13.

Notice pin 9 of Z11 is pulled up by R4Ø. Likewise, pins 3, 2, 1 and 6 are tied to ground. But pin 14 is used this time. In graphics, there is not a blank dot space between character rectangles.

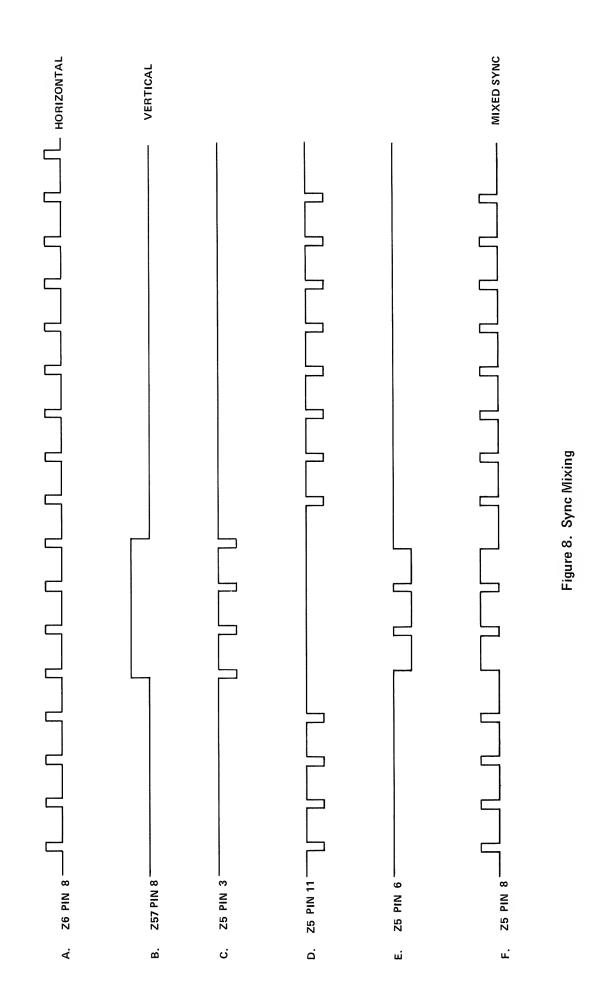

#### SYNC GENERATOR

The Sync Generator circuit accepts timing signals from the divider chain to develop horizontal and vertical sync pulses for the display. These pulses are used by the display to control the CRT's electron beam.

The sync pulses are generated by logic which operate like linear elements.